数码相机是一种电子成像设备,它承担将景物影像转换成电子数字图像的任务。近年来,数码相机技术的发展十分迅速。除光学成像系统、电子控制技术的进步以外,在电子成像技术方电信的技术进展也十分显著,不仅在电子成像芯片的元件类型和像素集成度上,而且在感光成像单元的排列结构、色光分解原理等方面都不断有新技术出现。本文将对其中一些相关技术进行比较和分析,同时,还对数码相机在电信前领域的应用进行讨论。

一、 电子成像芯片的元件类型

目前,在数码相机上应用的感光成像芯片主要有:CCD(电荷耦合器件)、CMOS(互补金属氧化物半导体器件)以及JFET(结型场效应管器件)3种。这3种器件完成对光学图像的光电转换,使之成为电子图像,三者在这一点上是共同的。图1为CCD、CMOS和JFET的成像芯片的外观。

作为成像器件,面阵型CCD发展电信较长,技术较为成熟,是目前在数码相机上应用量最大的成像器件。成像质量优良是CCD的优势,但制造技术复杂,成本相对较高,在提升芯片像素数的同时保持成像质量的要求下,继续提高像素数有一定难度;由于CCD器件在不成像时依然需要保持加电的工作状态,因而其耗电量相对较高。

CMOS用于电子成像的时间不很长,其成像质量提高迅速,综合性能接近CCD。其优点是制造技术相对简单,芯片尺寸和成品率的提高受限较少。此外,CMOS只在成像时才工作,耗电量较低。每个感光单元具备独立的电荷信号向电压信号转换电路,使图像信号的生成较为简单且速度较快。但CMOS在成像时需要重新建立工作所必需的电压/电流状态,状态的频繁变化会产生附加热量,导致噪声信号而影响图像品质。

JFET是由Nikon公司新近推出的成像器件,从其介绍的性能上看,这种器件突出的优势在于成像速度高。在Nikon的D2H单反数码相机上,快门时差仅为37毫秒、每秒8帧的连拍性能都与这种器件的特点相关。据称,这种器件同样具有耗电低、集成度高的优点。目前,在D2H单反数码相机上的JFET器件为410万像素。

二、 像素数与图像分辨率

1. 芯片尺寸和像素数

电子成像芯片上集成了大量感光单元,成像芯片接收到光学影像以后,每个感光单元将光信号转换成电信号。显然,芯片上的感光单元数越多,光学图像被“分割”成的像素数就越多,就有可能采集到更精细的图像细节。提高成像芯片的感光单元数(像素数)是制造厂商追求的目标之一。

但是,像素数高并不一定意味着图像质量优秀。这是因为,电子成像器件具有这样的特性,即:在其接收到的光量较低时,伴随图像信号的噪声信号会相对上升,而且所产生的电信号与光量之间是非线性关系,这些都会导致图像质量下降。在感光成像总面积保持不变的情况下,一味地提高感光单元(像素)的数量,则每个感光单元的面积必然下降,接收到的光量相对较少,信噪比下降。如果采用降低光圈指数、降低快门速度的方法提高整体曝光量,又可能使图像高光部分出现某种程度的过度曝光而损失影调层次。一些数码相机的评测报告中,在芯片尺寸和其他技术指标不变的前提下,像素数从300万提高到500万,确实存在图像质量下降的现象。

采用增大感光芯片总体面积的方法,可以增大每个微型感光单元的面积,或者在提高像素数的情况下,感光单元的面积不缩小,从而保证成像质量。但这会导致成品率降低,相对提高了成本,对民用型数码相机而言,这种做法并不十分明智。因此,在像素数、成像质量和成本三者之间寻找合适的平衡点,是厂商需要仔细把握的。

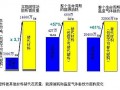

目前常用的感光芯片尺寸有:按对角线长度计算的1/2.7英寸、1/1.8英寸、2/3英寸、3/4英寸等;也有与135画幅一致的“全画幅”芯片(24毫米×36毫米)。常见的画幅宽高比有4∶3和3∶2。图2为宽高比4∶3下的4种画幅芯片面积比较,面积最大的底层为“135”画幅。

通过芯片成像面积,利用像素数数据,可以计算出每个感光单元的理论面积。由于感光单元旁边具备电荷传输和控制电路,其实际面积比理论值还要小。

(待续)